# **USER'S MANUAL**

# 4MEG VIDEO Model 12 Revision 4.2

6 November 2000

For use with: 4MEG VIDEO Model 12 Rev. 4.2

Copyright © 1995 EPIX, Inc. All Rights Reserved

EPIX, Incorporated 381 Lexington Drive Buffalo Grove, IL 60089 USA Tel -847 465 1818 Fax -847 465 1919 epix@epixinc.com

Image Processing Products For Research and Industry

EPIX, Incorporated 381 Lexington Drive Buffalo Grove, IL 60089 USA Tel -847 465 1818 Fax-847 465 1919 epix@epixinc.com

Image Processing Products For Research and Industry No part of this document may be reproduced, transmitted, photocopied, or translated into another language without the written consent of EPIX, Inc. Information in this document is subject to change without obligation or notice. EPIX, Inc. makes no warranty of any kind with regard to this document, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. EPIX, Inc. assumes no responsibility for any errors that may appear in this document. EPIX, Inc. reserves the right to make changes to the specifications of hardware and software at any time, without obligation or notice. 4MIP, SVIP, XCIP, XCAP, 4MEG VIDEO, 1MEG VIDEO, SILICON VIDEO MUX, QUICK SET VIDEO, 12-7MUX, IMAGE MEMORY EXPANSION, COC40, and COC402 are trademarks of EPIX, Inc. EPIX, SILICON VIDEO, and PIXCI are registered trademarks of EPIX, Inc. Other brand, product, and company names are trademarks or registered trademarks of their respective owners. Printing: 6 November 2000

| <b>©</b> EPIX <sub>®</sub> |  |

|----------------------------|--|

©EPIX.

### 1. Installation and Features

This manual refers to both the 4MEG VIDEO Model 12 Revision 4.0 and 4.1. The term 4MEG VIDEO or Model 12 will be used to refer to the 4MEG VIDEO Model 12.

The "PC memory base address" refers to the 64K address segment that is used by the 4MEG VIDEO Model 12. The default is 0xD0000. The prefix "0x" denotes a hexadecimal number. Reference is made to EPIX' 4MIP software.

### 1.A Unpacking and Static Warning

The 4MEG VIDEO Model 12 is packed in a static dissipative bag. Please keep the bag and box in which the board was shipped should the need arise to return the board.

Prior to opening the bag, place the bag near the PC into which the board will be installed. Holding the bag and the PC should dissipate any static charge that may have been created transporting the board to the PC. A static free area for installation is adviseable or use a wrist strap that is connected to the PC or to a static workstation.

# 1.B Memory, I/O, Interrupt, and 8/16 Bit Cycle Considerations

The 4MEG VIDEO Model 12 uses memory addresses, I/O port addresses, and an interrupt of the PC or PC/AT bus. System problems may result when the Model 12 is accessed by software if RAM is present in the memory segment that the Model 12 will occupy, if I/O ports that the Model 12 uses are used by other devices, or if the selected interrupt level is used by other PC devices. Devices that use these addresses or interrupt must either be removed, changed, or the Model 12 must be configured to avoid conflict.

The user should determine if any other peripherals in the system will interfere with the Model 12. Some 16 bit VGA graphics adapters running in 16 bit mode use memory at 0xD0000. LIM memory may also cause a conflict if it is enabled. Memory management software should be configured to avoid using the same memory segment that the Model 12 is using. The DOS program "MSD" can be used to report possible memory and I/O port conflicts. Read the "In Case of Trouble" chapter to help resolve installation problems.

Jumpers select the memory segment, I/O base address, and interrupt level. The standard base memory address is 0xD0000, the standard base I/O port address is 0x280, and the standard interrupt is IRQ level 3. 4MIP assumes these settings unless configured otherwise. Note that if the Model 12 was ordered from the factory with nonstandard memory address, I/O port, or interrupt level, the board will be set with these options. To operate 4MIP with other than the standard settings, refer to the 4MIP manual for details.

The memory addresses used by Model 12 are selected by the MEM jumper. Placing the MEM jumper over the two pins marked "xD" selects the 0xD0000 thru 0xDFFFF address range. Placing the MEM jumper over the two pins marked "xE" selects the 0xE0000 thru 0xEFFFF address range. To operate 4MIP with a memory base other that 0xD0000, refer to the 4MIP manual for details.

The I/O addresses used by Model 12 are selected by the I/O jumper. Placing the I/O jumper over the two pins marked "x280" selects the 0x280 thru 0x283 address range for the I/O ports. Placing the I/O jumper over the two pins marked "x290" selects the 0x290 thru 0x293 address range for the I/O ports. To operate 4MIP with an I/O port base other that 0x280, refer to the 4MIP manual for details.

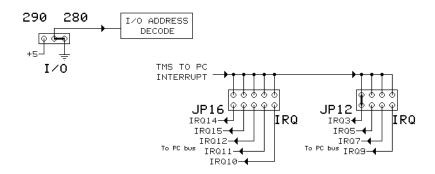

The interrupt request level is selected by two IRQ jumpers. Jumper JP12 selects one of IRQ 3, 5, 7, or 9. Jumper JP16 selects one of IRQ 10, 11, 12, 14, or 15. Note that level 2 is mapped to level 9 on the 16 bit AT bus and that interrupts higher than 9 are not available in an 8 bit PC bus slot. 4MIP can operate without using interrupts.

Refer to the 4MIP User's Manual for details.

If the video input is from the composite video of a RS-170 camera, the standard jumper settings for the Model 12 do not need to be changed. If this is not the configuration that will be used, see the "Connections" and the "Jumpers" chapters before proceeding. Otherwise, perform the installation steps below.

### 1.C Installation

The 4MEG VIDEO Model 12 is packed in a static dissipative bag. Please keep the bag and box in which the board was shipped should the need arise to return the board.

Prior to opening the bag, place the bag near the PC into which the board will be installed. Holding the bag and the PC at the same time should dissipate any static charge that may have been created transporting the board to the PC. A static free area for installation is adviseable and the use of a wrist strap that is connected to the PC or to a static workstation is suggested.

- Run MSD to check for possible I/O and memory conflicts.

- 2. Install 4MIP according to the instructions in the 4MIP manual.

- 3. Follow the directions for the PC's cover removal (if one is used with the PC) and remove the cover.

- 4. Locate a vacant ISA or EISA slot and remove the metal bracket and screw covering the back panel slot with which it is aligned.

- 5. Gently ease the imaging board into the connectors. The 4MEG VIDEO Model 12 has 16 bit bus fingers, but it can be installed in an 8 bit slot. 16 bit bus transfers will not be possible if it is installed in an 8 bit slot.

- 6. Replace the screw to secure the imaging board in the selected slot.

- 7. Connect the video input to the VIN cable.

- 8. Connect the GREEN cable to the monitor input or use the VGA monitor display capability of 4MIP.

- 9. Connect the DB25 plug on the cable into the DB25 receptacle on the Model 12.

- 10. Operate 4MIP and check for proper operation with the camera.

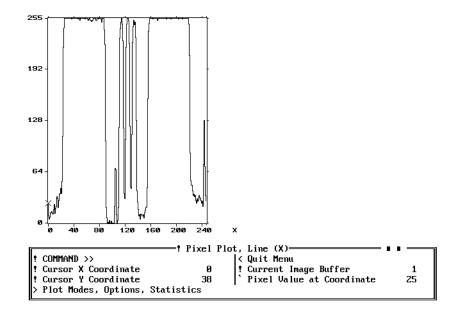

- 11. Perform a histogram to check for grey levels near 255 in the brightest area of the image and grey levels near 0 in the darkest area of the image. If the 255 and 0 grey levels are not achieved, adjustment of the "GAIN" and "CLMP" potentiometers may be required. See the **Gain and Black Level Adjustment** chapter.

- 12. Replace the PC's cover.

### 1.D Features

The Model 12 is a flexible image acquisition, processing, and display board for the PC or PC/AT bus. The TMS320C25 processor is available for image processing when not controlling video timing. TMS320C25 program RAM is loaded by the PC/AT and allow the processor to be programmed for specific applications. The program RAM may be replaced by ROM for stand-alone applications (no PC/AT host).

A user programmable microsequencer allows for digitization and display of video from standard video sources (RS-170, CCIR, RS-343). Video from unusual video sources such as Dalsa CL-Cx series, KODAK MEGAPLUS, and line scan cameras can also be digitized. Lines of up to 8000 pixels may be digitized. A standard Model 12 can operate with pixel clocks up to 30 MHz. Options allow pixel clocks up to 50 MHz and lines with up to 31,000 pixels.

The PC data bus interface is 16 bits wide and supports both 8 and 16 bit memory access. The Model 12 can be installed in an 8 bit PC bus slot, but will have slower memory access. The bus can run with zero wait states during image memory access for maximum throughput during image processing operations or file transfers (this may not operate on some clones).

For display, three look-up tables drive red, green and blue digital to analog converters to provide pseudo-color output. Video sync is on the green output. A cursor generator is also provided, giving a full screen cross-hair cursor, a 64 x 64 bit mapped cursor, or both. With 4MIP and 4MOBJ, a box of arbitrary size can be drawn with the cursor.

The video input is digitized to 8 bits. A DC restoration circuit clamps the input video signal to an adjustable black level. Clamping may be triggered during the video back porch or the horizontal sync, for cameras that do not provide a back porch. Potentiometers are used to adjust video gain and black level. Alternatively, connections are provided to accept 8 bit digital data or two 8 bit digital pixels for up to 16 bit input.

A sync stripper is used to detect video synchronizing signals from composite video sources and to generate a clamp signal.

The image memory starting address of each line of video is set by the TMS320. During image capture, this allows interlacing lines in the memory, which can speed up image processing operations. During display, this allows panning and scrolling of the image.

Connections are available for monochrome video input. Video outputs are green (with sync), red, and blue.

The standard Analog Module provides composite sync or horizontal sync input, vertical sync input, and pixel clock input, a TTL level trigger input for external event synchronization, a TTL level trigger output, pixel clock output, horizontal sync output, and vertical sync output.

The optional Pixel Clock and Video Four Input Multiplexer Module provides four pixel clock and video inputs. A jumper on the module allows selection of external input or external output.

### 1.E Related EPIX Documents

- 1. Camera Compatibility Guide. Lists cameras that have been interfaced to EPIX' imaging boards and have an application note or interface user manual available from EPIX.

- 2. PC Configuration Tips. Provides information on installation of EPIX hardware and software in the PC environment.

- 4MIP User's Manual. Provides information on the use of 4MIP menu driven programs for the Model 12.

- 4MOBJ Object Code Library Reference Manual and PXIPL Image Processing Object Code Library Reference Manual. Describe object code library used with the Model 12.

- Software Directory. Third party software descriptions for use with the 4MEG VIDEO Model 12 and other EPIX products.

#### 1.F Related Documents

- TMS320C2x User's Guide, 1604907-9721 revision B, December 1990. Texas Instruments, Incorporated.

- Brooktree, Graphics and Imaging Product Databook 1993. Brooktree Corporation.

©EPIX.

### 2. Connectors

### 2.A DB25 Connector

The DB25 (D-suBminature) connector is located at the right hand edge of the Model 12. When the Model 12 is installed in a PC chassis, it is accessible at the back of the PC chassis. The connector is a female 25 pin D-Subminiature connector, AMP PN 749414-1. Eight pins are connected from the Model 12 motherboard to the DB25 (CON7). These eight pins carry video in, green out, red out, blue out and a ground pin for each of them. All other pins of the DB25 connector are connected to a 40 pin socket connector (CON6) that is located adjacent to the DB25. Some of the pins of CON6 provide power, the rest provide connections for various signals that connect to and from the Model 12. CON6 allows the pins that are not connected directly to the Model 12 motherboard to be used for purposes that are defined by the module connected to CON6.

The standard module connected to CON6 is the Analog Module. The Analog Module on the Model 12 provides the DB25 with the same signals that were on the 4MEG VIDEO Model 10 DB25 connector. An optional module that may be connected to CON6 is the Pixel Clock and Video Four Input Mux. When a module other than the Analog Module or the Pixel Clock and Video Four Input Mux Module is installed, the module's manual provides DB25 connector information.

If the only video signals required are video in, green out, red out, and blue out, or a subset of these signals, no module is required.

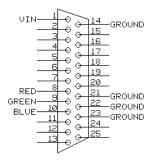

Figure 2-1. DB25 Connector - no module installed

### 2.A.1 Motherboard DB25 Signal Descriptions

VIN (or VIDEO IN) on pin 1 of the DB25 connector, is the analog video input. The signal level should be 1 volt peak to peak with the video portion positive and the sync tips negative. The signal input level should be 0.714 volt peak to peak if sync is not present in the video. The minimum composite video input signal that can be amplified to provide 0 thru 255 grey levels is 0.4 volts peak to peak. The maximum composite video input signal that can be amplified to provide 0 thru 255 grey levels is 2.5 volts peak to peak. The input is terminated in  $75\Omega$  to ground with the TERM (JP5) jumper. Pin 14 is the ground connection for VIN.

**RED,** on pin 8 of the DB25 connector, is the red video output signal of the BT453 RAMDAC. The signal level is 0 to 0.714V terminated in  $75\Omega$  to ground. Pin 21 can be used for the coaxial cable ground connection.

GREEN, on pin 9 of the DB25 connector, is the green video output signal of the BT453 RAMDAC with composite sync added. The signal level is 0 to 1V terminated in  $75\Omega$  to ground. Pin 22 can be used for the coaxial cable ground connection.

**BLUE,** on pin 10 of the DB25 connector, is the blue video output signal of the BT453 RAMDAC. The signal level is 0 to 0.714V terminated in  $75\Omega$  to ground. Pin 22 can be used for the coaxial cable ground connection.

### 2.A.2 Analog Module DB25 Signal Descriptions

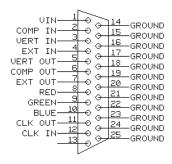

Figure 2-2. DB25 Connector - Analog Module installed

In the descriptions that follow, reference is made to jumpers and potentiometers which are described in detail in the **Jumpers and Pixel Clock Generator Module** and **Adjustments** chapters that follow.

**COMP IN,** on pin 2 of the DB25 connector, is the composite sync input or the horizontal sync input. This input is connected to the SSEL (JP1) jumper and the HSEL (JP7) jumper on the M12 motherboard. Signal levels are 0.286V to 4V peak to peak, with negative sync. In some applications a TTL input can be used. It is terminated in  $75\Omega$  to ground with the CSTERM (J2) jumper. Pin 15 is the ground connection for COMP IN.

**VERT IN,** on pin 3 of the DB25 connector, is the vertical sync input which is compared to a +1.4 volt or -1.4 volt level (selected with the VC C (J4) jumper). The voltage level should be 2.5 volts peak to peak. The input is terminated in  $75\Omega$  to ground with the VDTERM (J1). Pin 16 can be used for the coaxial cable ground connection.

**EXT IN,** on pin 4 of the DB25 connector, is the TTL trigger input which interrupts the TMS320C25. This signal is terminated with  $330\Omega$  to +5 volts and  $390\Omega$  to ground. This termination provides a TTL logic 1 when no signal is driving the input. A TTL high to low transition generates a level 1 interrupt to the TMS320C25. The external input allows the TMS320C25 to sense an external event such as a button press, or a part in position indicator. Pin 17 can be used for the coaxial cable ground connection.

**VERT OUT,** on pin 5 of the DB25 connector, is the vertical sync output. A driver provides a signal level of 0 to -4V into  $75\Omega$ . This signal is low when active. Pin 18 can be used for the coaxial cable ground connection.

**COMP OUT,** on pin 6 of the DB25 connector, is the composite sync output. The source of this signal is selected with J3 on the Analog Module. The source can be either from the sync generated on the Model 12 (M12 position of J3), or from the V8SYN input on the V8 connector (the V8 position of J3). When the Model 12 generated sync is selected, the signal level is 0 to -4V with a  $75\Omega$  termination to ground. When the V8 connector is selected, COMP OUT has the same level and timing as the V8SYN input. This is low when active. Pin 19 can be used for the coaxial cable ground connection.

**EXT OUT**, on pin 7 of the DB25 connector, is the inverted TTL output from the TMS320C25 XF pin. The external output signal is the inverted TMS320C25's external flag pin. This pin is reset and set using the SXF and RXF commands (TMS320C25 assembly language). The signal output is inverted from the sense of the software command; execution of the SXF command results in EXT OUT low; execution of the RXF command results in the EXT OUT high. The external output allows the TMS320C25 to control an external event such as a strobe flash, or a laser pulse. See the TMS320C25 User's Guide for more information on these two commands.

**CLK OUT,** on pin 11 of the DB25 connector, is a TTL pixel clock output buffered by a 74BCT244 on the Analog Module. Pin 23 can be used for the coaxial cable ground connection.

**CLK IN,** on pin 12 of the DB25 connector, is a pixel clock input, terminated in  $75\Omega$  to ground with the CKPTERM (J6) jumper. For optimal operation this should be a 50% duty cycle signal. Pin 25 can be used for the coaxial cable ground connection.

Pin 13 is not used on the Analog Module.

### 2.A.3 Pixel Clock and Video Four Input Mux Module DB25 Signal Descriptions

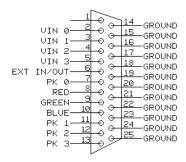

Figure 2-3. DB25 Connector - Pixel Clock and Video Four Input Mux Module installed

In the descriptions that follow, reference is made to jumpers and potentiometers which are described in detail in the **Jumpers and Pixel Clock Generator Module** and **Adjustments** chapters that follow.

VIN 0-3, on pins 2 thru 5 of the DB25 connector, are composite video inputs 0 thru 3. One of these inputs is selected to drive the video input of the Model 12. (or VIDEO IN) on pin 1 of the DB25 connector, is the analog video input. The signal level should be 1 volt peak to peak with the video portion positive and the sync tips negative. The signal input level should be 0.714 volt peak to peak if sync is not present in the video. The minimum composite video input signal that can be amplified to provide 0 thru 255 grey levels is 0.4 volts peak to peak. The inputs are terminated in  $75\Omega$  to ground with jumpers V0-3. Pins 14 thru 17 are the ground connections for VIN 0-3.

**EXT IN/OUT,** on pin 6 of the DB25 connector, is selected to be either "EXT IN" or "EXT OUT" by jumper JA1. The function of the pin is as described for the Analog Module above. Pin 18 is used for the coaxial cable ground connection.

**PK** 0-3, on pins 7, 11, 12, and 13 of the DB25 connector, are the pixel clock inputs for VIN 0-3 respectively. They can be terminated in  $75\Omega$  to ground with jumpers K0-3. For optimal operation they should be 50% duty cycle signals. Pins 19, 23, 24, and 25 are used for the coaxial cable ground connections.

The Pixel Clock and Video Four Input Mux Module is controlled by MC0 and MC1 from the V8 connector. A PKTOV8 board with 10 position header mounts in the V8 connector. The standard chip at location B8 is replaced with one that drives the MC0 and MC1 signals in the 4 modes of operation of the V8 connector. A ten conductor cable connects to the CON1 header on the PKTOV8 board to the CON1 header on the Pixel Clock and Video Four Input Mux Module. The header at each end of the cable is wired so that the cable may be installed with either orientation.

#### 2.B LUT Connector

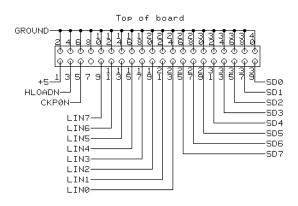

The Look Up Table (LUT) connector at location A12 (also marked CON4) has a video rate 8 bit data output and an 8 bit data input. The data output is registered data from the analog to digital converter (SD7-0). The data input is to an 8 bit register (LIN7-0). The LUT connector can be used to perform real time operations on digital video such as: look up table, bit packing, or arithmetic operations. The connector provides an inverted pixel clock output, a horizontal load signal output, +5 volt power, and a ground pin for each signal pin. When a cable connection is not made to the LUT connector, a connector and small printed circuit board are installed. The board mounted connector is an AMP 10468-4. The mating connector for a cable is AMP 111196-9. It uses 40 conductor ribbon cable with conductors on 0.25 centerline spacing. The mating connector for a printed circuit board is AMP 104078-2.

Figure 2-4. LUT Connector

### 2.B.1 LUT Signal Descriptions

All signals are TTL, single ended, and unterminated.

$SD7 \rightarrow SD0$  are the 8 registered outputs from the A-D converter. SD7 is the most significant bit.

$LIN7 \rightarrow LIN0$  are the 8 data inputs to the register from the LUT connector. LIN7 is the most significant bit.

HLOADN is an active low signal used to indicate the start of a horizontal line. HLOADN loads the HCM address and is driven by a GAL22V10B with 15 ns maximum propagation delay from the noninverted pixel clock. If the M12 is ordered for pixel clocks of greater than 30 MHz, an 8 ns maximum propagation GAL22V10B part is intstalled. It has three loads on the M12, and should not drive more than one load.

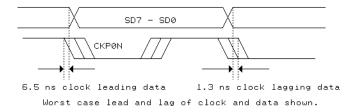

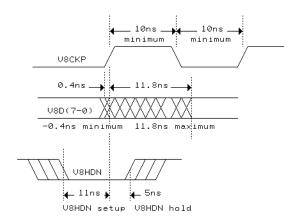

CKP0N is an inverted pixel clock. It has one load on the M12. A timing diagram for the LUT connector follows.

Figure 2-5. LUT Timing

### 2.C V8 Connector

The V8 connector at location A3 (also labelled CON3) provides bidirectional 8-bit image data to/from the image memory. The connector also provides the signals on the Model 10's Digital Interface Connector, Digital Data Interface Connector, and optional VGA Output. The board mounted connector is an AMP 10468-4. The mating connector for a cable is AMP 111196-9. It uses 40 conductor ribbon cable with conductors on 0.25 centerline spacing. The mating connector for a printed circuit board is AMP 104078-2.

Along with 8 data bits, the interface accepts or drives horizontal sync, vertical sync, and pixel clock. The 4 mode control bits are outputs. A composite sync input, V8SYN, is used to pass sync to the M12's Analog Module and if selected by jumper J3 on the Analog Module, V8SYN is connected to the composite sync output of the M12 DB25 connector.

Two bits in register T13 select one of four modes of operation for the V8 connector. The modes provide for external pixel clock, horizontal, and vertical timing from the DB25 via the Analog Module; VGA data output; data out; and data in. See the description of register T13, V8 Control 1 and 0 bits in the **Registers and Horizontal Control Memory** chapter for detailed information.

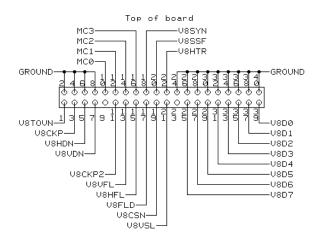

Figure 2-6. V8 Connector

# 2.C.1 V8 Connector Signal Descriptions

The following are unterminated, single ended, TTL signals.

V8TOVN is an active low output signal that indicates that V8D7 thru V8D0 have pixel data for display to the VGA adapter.

V8CKP is a bidirectional pixel clock.

V8HDN is a bidirectional, active low, horizontal drive signal.

**V8VDN** is a bidirectional, active low, vertical drive signal.

MC3, MC1, MC0 are the outputs of bits 3 thru 0 of register T12 of the TMS320C25 and are used to control cameras and digital interfaces.

V8CKP2 is a pixel clock output.

V8VFL is an active low, vertical force low output that indicates vertical blanking.

**V8HFL** is an active low, horizontal force low output that indicates horizontal blanking.

**V8FLD** is a video field output.

V8SYN is an active low, composite sync input used to drive an external monitor and to genlock the M12 during display.

V8CSN is a composite sync input used to drive an external monitor and for the M12 to genlock to for display.

**V8SSF** is the output of the sync stripper field signal.

**V8VSL** is the output of the VSPIL signal from the HCM.

**V8HTR** is the output of the HTRIG signal from the HCM. **V8D7** → **V8D0** are the bidirectional, 8 data bits, V8D7 being the most significant bit.

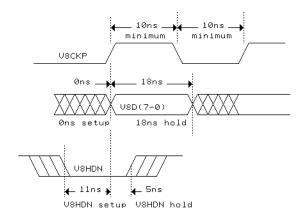

V8 Connector timing diagrams are shown below for pixel clock, data, horizontal, and vertical inputs and outputs.

Figure 2-7. V8 Connector Pixel Clock, Data, and Horizontal Input Timing

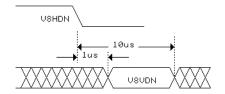

V8VDN must be stable between 1us and 10us after the falling edge of V8HDN.

Figure 2-8. V8 Connector Horizontal and Vertical Input Timing

Figure 2-9. V8 Connector Pixel Clock, Data, and Horizontal Output Timing

©EPIX.

# 3. Jumpers and Pixel Clock Generator Module

# 3.A Motherboard Standard Jumper Settings

Prior to shipping the 4MEG VIDEO Model 12 to customers, EPIX configures the jumpers on the motherboard and the Analog Module or Pixel Clock and Video Four Input Multiplexer Module to the standard positions listed in Tables 3-1, 3-2, and 3-3. With the jumpers in these positions the Model 12 is configured to genlock to a composite RS-170 or CCIR video source terminated in 75 ohms. Note that it is assumed that the user is facing the component side of the board with the PC bus fingers pointing down. Block diagrams are shown for the analog section jumpers and potentiometers, and for the other jumpers in this section. If the Model 12 is configured with a different module than the Analog Module or Pixel Clock and Video Four Input Multiplexer (4PVINAM) Module, consult the module's manual for additional configuration information.

| Label | Jumper | Position     | Mark | Comment                                               |

|-------|--------|--------------|------|-------------------------------------------------------|

| SSEL  | JP1    | Right        | V    | Video input to sync stripper.                         |

| MEM   | JP4    | Left         | D    | Decode PC bus 0xD segment for memory.                 |

| TERM  | JP5    | On Both Pins |      | Video input terminated in 75 ohms to ground.          |

| PCLK  | JP6    | Left         | В    | Master mode pixel clock is PC bus 14.318 MHz.         |

| HSEL  | JP7    | Right        | S    | Genlock to composite sync from sync stripper.         |

| 0WS   | JP10   | On one pin   |      | Disable PC bus 0 wait states.                         |

| IRQ   | JP12   | Left         | 3    | Select IRQ3 interrupt.                                |

| I/O   | JP13   | Right        | x280 | Select 0x280 as PC bus I/O base address.              |

| CLMP  | JP15   | Left         | M    | Video clamped by sync stripper or programmable clamp. |

| DCC1  |        | On one pin   |      | DC restoration used.                                  |

| DCC2  |        | On one pin   |      | DC restoration used.                                  |

TABLE 3-1. Motherboard Standard Jumper Settings

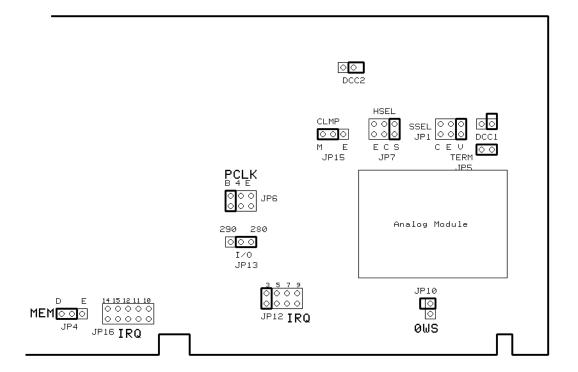

Figure 3-1. Motherboard Jumper Locations and Standard Settings

### 3.B Motherboard Jumper Descriptions

SSEL JP1 selects one of three inputs to the sync stripper: composite video input from the DB25 connector, composite sync from the V8 connector, composite sync input from the Analog Module and the DB25 connector. The selected signal is connected to the sync stripper input.

| SSEL Position | Mark | Select                                         |

|---------------|------|------------------------------------------------|

| Left          | С    | Analog Module composite input from DB25 pin 2. |

| Middle        | Е    | V8SYN from pin 18 of the V8 connector.         |

| Right         | V    | Composite video input from DB25 pin 1.         |

|               |      | 1 1                                            |

MEM JP4 selects the memory base address on the PC bus. The base address is 0xE0000 or 0xD0000, unless specified otherwise when ordering. If a different base address has been requested, the socketed IC at K13 (to the right of the MEM jumper) will be marked with the two addresses.

| MEM Position | Mark | Memory base address. |

|--------------|------|----------------------|

| Left         | D    | 0xD0000              |

| Right        | Е    | 0xE0000              |

TERM JP5 terminates the video input in 75 ohms to ground. Installing the jumper on one pin and leaving the other pin unconnected selects a high impedance (9K ohms) which is used when another device terminates the video input.

| TERM Position | Termination                         |  |

|---------------|-------------------------------------|--|

| On both pins  | 75 ohms to ground.                  |  |

| On one pin    | High impedance (9K ohms to ground). |  |

PCLK JP6 is used to select the pixel clock source when the Model 12 is in master sync mode (generating video timing).

| PCLK Position | Mark | Master mode pixel clock.      |

|---------------|------|-------------------------------|

| Left          | В    | PC Bus 14.318 MHz.            |

| Middle        | 4    | Pixel clock generator module. |

| Right         | Е    | V8 or Analog Module and DB25. |

HSEL JP7 is used to select the horizontal or sync source when the Model 12 is genlocked or when using an external pixel clock, and selects the sync source for the programmable video timing detector. The source can be the sync stripper, COMP IN from the DB25 connector thru the Analog Module, or V8HDN from the V8 connector.

Select the "S" position (sync stripper output) with HSEL JP7 if timing information is to be derived from composite video or composite sync and when using a camera pixel clock with composite video as the sync source.

Select the "E" position of HSEL JP7 when the video timing source is the V8 connector.

Select the "C" position of HSEL JP7 when a TTL level composite sync or horizontal sync is connected to the DB25 COMP IN signal thru the Analog Module.

| Č             |      | 6                                     |

|---------------|------|---------------------------------------|

| HSEL Position | Mark | Horizontal or sync source.            |

| Left          | Е    | V8HDN from V8 connector.              |

| Middle        | С    | COMP IN from DB25 thru Analog Module. |

| Right         | S    | Sync stripper output.                 |

0WS JP10 connects to the PC bus No Wait State line and shortens PC bus accesses to image memory. Zero wait states may not work on some PCs.

| 0WS Position | Select                |

|--------------|-----------------------|

| On both pins | Zero wait states.     |

| On one pin   | Normal bus operation. |

**IRQ JP12** (and JP16) are used to select an interrupt on the PC bus. The positions are marked "3 5 7 9" and select one of the respective interrupts on the PC bus for use by the Model 12. Note that level 9 appears as level 2 in an 8 bit PC bus slot and note that interrupts higher than 9 are not available in an 8 bit PC bus slot.

| IRQ Position  | Mark | Select                    |

|---------------|------|---------------------------|

| Left          | 3    | IRQ3                      |

| 2nd from left | 5    | IRQ5                      |

| 3rd from left | 7    | IRQ7                      |

| 4th from left | 2    | IRQ9 (IRQ2 in 8 bit slot) |

| 5th from left | 10   | IRQ10                     |

| 6th from left | 11   | IRQ11                     |

| 7th from left | 12   | IRQ12                     |

| 8th from left | 15   | IRQ15                     |

| 9th from left | 14   | IRQ14                     |

**IRQ JP16** (and JP12) are used to select an interrupt on the PC bus. The positions are marked "14 15 12 11 10" and select one of the respective interrupts on the PC bus for use by the Model 12. Note that interrupts higher than 9 are not available in an 8 bit PC bus slot.

| IRQ Position  | Mark | Select |

|---------------|------|--------|

| Left          | 3    | IRQ14  |

| 2nd from left | 5    | IRQ15  |

| 3rd from left | 7    | IRQ12  |

| 4th from left | 2    | IRQ11  |

| 5th from left | 10   | IRQ10  |

The I/O jumper selects one of two base addresses for the four PC bus registers. The base I/O addresses are 0x280 or 0x290. Should the user request alternate I/O addresses, the socketed logic chip up and to the left of the I/O jumper will be labelled with the two addresses. The left jumper position will select the upper address.

| I/O Position | Mark | Select              |

|--------------|------|---------------------|

| Left         | x290 | 0x290 base address. |

| Right        | x280 | 0x280 base address. |

The **CLMP JP15** jumper selects one of three signals to clamp the video input signal from the DB25 connector. The left position (marked M) selects either the programmable HCM based clamp signal (T13, SYCL = 1) or the sync stripper burst signal as the clamp signal (T13, SYCL = 0). The right position (marked E) selects the signal selected by the HSEL (JP7) jumper. Leaving the jumper on just one of the three pins allows the clamp signal to be pulled to a logic 1 and not clamp the video input. This position is selected when the video input is DC coupled (see DCC1 and DCC2 jumper descriptions).

| CLMP JP15 Position | Mark | Select                          |

|--------------------|------|---------------------------------|

| Left               | M    | Sync stripper or HCM clamp.     |

| Right              | Е    | HSEL selected signal for clamp. |

DCC1 & DCC2 jumpers short two capacitors used in the DC restoration circuit. These jumpers should be placed on just one pin to allow DC restoration. When it is desired to use a camera with a DC coupled video output, the jumpers can be placed over both pins and the CLMP JP15 jumper placed on just one pin. Adjustment of the GAIN potentiometer may be required. See the Gain and Black Level Adjustment chapter for details.

| DCC1 & DCC2 Position | Select          |

|----------------------|-----------------|

| On both pins         | DC coupled.     |

| On one pin           | DC restoration. |

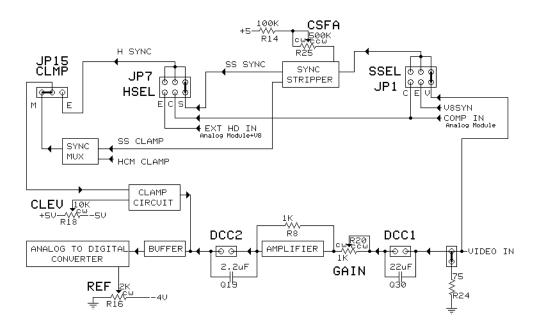

A block diagram of the analog input potentiometers and jumpers is shown in Figure 3-2.

Figure 3-2. Analog Input Potentiometers and Jumpers Block Diagram

A block diagram of the other jumpers on the Model 12 motherboard is shown in Figure 3-3.

Figure 3-3. Other Motherboard Jumpers

# 3.C Analog Module Standard Jumper Settings

Prior to shipping the 4MEG VIDEO Model 12 to customers, EPIX configures the jumpers on the Analog Module to the standard positions listed in the table below and shown in Figure 3-4. A jumper schematic diagram for the Analog Module is shown at the end of this section. See the section on the 4PVINAM Module for a description of the jumpers on that module.

| Label   | Jumper | Position     | Mark | Comment                                               |

|---------|--------|--------------|------|-------------------------------------------------------|

| VDTERM  | J1     | On both pins |      | Video drive input terminated in 75 ohms to ground.    |

| CSTERM  | J2     | On both pins |      | Composite sync input terminated in 75 ohms to ground. |

|         | J3     | M12          |      | Composite sync output from Model 12.                  |

| VD C    | J4     | Left         | -    | Vertical drive input compared to -1.4V.               |

| CK      | J5     | Left         | 1.4  | Pixel clock input compared to +1.4V.                  |

| CKPTERM | J6     | On both pins |      | Pixel clock input terminated in 75 ohms to ground.    |

**TABLE 3-2.** Analog Module Standard Jumper Settings

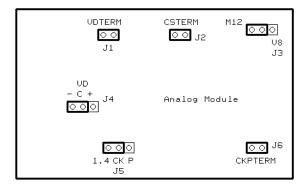

Figure 3-4. Analog Module Jumper Locations and Standard Settings

### 3.D Analog Module Jumper Descriptions

VDTERM J1 terminates the vertical drive input of the DB25 connector in 75 ohms to ground when installed on both pins. Placing the jumper on just one pin removes the 75 ohm termination and prevents the jumper from being lost. The termination is removed when more than one device is driven by a vertical drive source.

| VDTERM Position | Select                                               |

|-----------------|------------------------------------------------------|

| On both pins    | Terminate vertical drive input in 75 ohms to ground. |

| On one pin      | Remove 75 ohm termination.                           |

CSTERM J2 terminates the composite sync input of the DB25 connector in 75 ohms to ground when installed on both pins. Placing the jumper on just one pin removes the 75 ohm termination.

| CSTERM Position | Select                                               |

|-----------------|------------------------------------------------------|

| On both pins    | Terminate composite sync input in 75 ohms to ground. |

| On one pin      | Remove 75 ohm termination.                           |

OUTCS J3 selects the source of composite sync output to the DB25 connector from either the M12 composite sync circuit or from the V8SYN signal on the V8 connector. The V8SYN signal is used when digitizing from the Kodak MEGAPLUS digital interface. When V8SYN is a sync source for the board to genlock to in display mode, and to drive the video monitor while digitizing, it prevents the monitor from losing sync.

| OUTCS J3 Position | Mark | Select                                         |

|-------------------|------|------------------------------------------------|

| Left              | M12  | M12 sync circuit drives composite sync output. |

| Right             | V8   | V8SYN used to drive composite sync output.     |

VD C J4 selects the voltage used for comparison to the DB25 connector vertical drive input. Some video systems use a vertical drive signal that is +4 volts when not in vertical drive and 0 volts during vertical drive. Some video systems use a vertical drive signal that is 0 volts when not in vertical drive and -4 volts during vertical drive. The two jumper positions select either a positive or negative 1.4 volt signal as the voltage for the vertical drive comparator. The comparator output is read by the TMS320C25 to determine when vertical drive occurs. It is also used with the DB25 horizontal input to create composite sync when the Model 12 is driven with separate external vertical and horizontal drive.

Note that the negative position should be selected when using an external pixel clock and not using external vertical drive.

| VD C Position | Mark | Select                                                    |

|---------------|------|-----------------------------------------------------------|

| Left          | -    | Negative 1.4 volt for comparison to vertical drive input. |

| Right         | +    | Positive 1.4 volt for comparison to vertical drive input. |

CK J5 selects the voltage used for comparison of the DB25 connector pixel clock input. The two jumper positions select either a positive 1.4 volt signal or a potentiometer for comparison to the pixel clock input. The 1.4 volt position can be used with a pixel clock that has TTL levels. Some camera pixel clock outputs do not have TTL levels. See the Adjustments chapter for details.

| CK Position | Mark | Select                                                 |

|-------------|------|--------------------------------------------------------|

| Left        | 1.4  | Positive 1.4 volt for comparison of pixel clock input. |

| Right       | P    | Potentiometer for comparison of pixel clock input.     |

CKPTERM J6 terminates the DB25 pixel clock input in 75 ohms to ground. Installing the jumper over a single pin removes the 75 ohm input termination.

| CKPTERM Position | Select                                             |

|------------------|----------------------------------------------------|

| On both pins     | Pixel clock input terminated in 75 ohms to ground. |

| On one pin       | Pixel clock termination removed.                   |

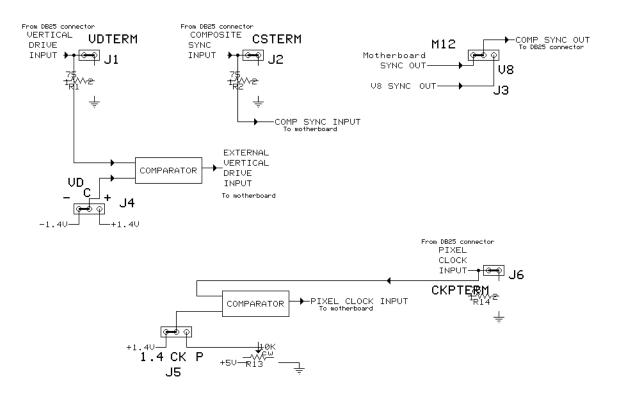

A block diagram of the analog module potentiometers and jumpers is shown in Figure 3-5.

Figure 3-5. Analog Module Potentiometers and Jumpers Block Diagram

# 3.E Pixel Clock and Video Four Input Multiplexer Jumper Settings

Prior to shipping the 4MEG VIDEO Model 12 to customers, EPIX configures the jumpers on the Pixel Clock and Video Four Input Multiplexer Module (4PVINAM) to the standard positions listed in the table below and shown in Figure 3-6. A jumper schematic diagram for the 4PVINAM Module is shown at the end of this section.

| Label | Jumper | Position     | Mark | Comment                                              |

|-------|--------|--------------|------|------------------------------------------------------|

| V0    |        | On both pins |      | Video input 0 terminated in 75 ohms to ground.       |

| V1    |        | On both pins |      | Video input 1 terminated in 75 ohms to ground.       |

| V2    |        | On both pins |      | Video input 2 terminated in 75 ohms to ground.       |

| V3    |        | On both pins |      | Video input 3 terminated in 75 ohms to ground.       |

| K0    |        | On both pins |      | Pixel clock 0 input terminated in 75 ohms to ground. |

| K1    |        | On both pins |      | Pixel clock 1 input terminated in 75 ohms to ground. |

| K2    |        | On both pins |      | Pixel clock 2 input terminated in 75 ohms to ground. |

| К3    |        | On both pins |      | Pixel clock 3 input terminated in 75 ohms to ground. |

|       | J5     | Right        | 1.4  | Pixel clock input compared to +1.4V.                 |

| IN    | JA1    | Left         | OUT  | External input to Model 12 motherboard.              |

**TABLE 3-3.** Pixel Clock and Video Four Input Multiplexer Jumper Settings

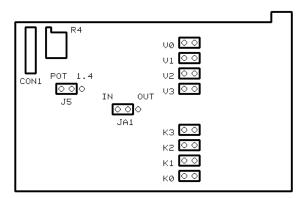

Figure 3-6. Pixel Clock and Video Four Input Multiplexer Jumper Locations

### 3.F Pixel Clock and Video Four Input Multiplexer Jumper Descriptions

**V0-V3** terminates the video input 0 to 3 from the DB25 connector in 75 ohms to ground when installed on both pins. Placing the jumper on just one pin removes the 75 ohm termination and prevents the jumper from being lost. The termination is removed when the video input is not at the end of a coaxial cable.

| V0-V3 Position | Select                                               |

|----------------|------------------------------------------------------|

| On both pins   | Terminate vertical drive input in 75 ohms to ground. |

| On one pin     | Remove 75 ohm termination.                           |

K0-K3 terminates pixel clock input 0 to 3 from the DB25 connector in 75 ohms to ground when installed on both pins. Placing the jumper on just one pin removes the 75 ohm termination and prevents the jumper from being lost. The termination is removed when the pixel clock input is not at the end of a coaxial cable.

| K0-K3 Position | Select                                            |

|----------------|---------------------------------------------------|

| On both pins   | Terminate pixel clock input in 75 ohms to ground. |

| On one pin     | Remove 75 ohm termination.                        |

CK selects the comparison voltage for the pixel clock to be either a +5 to 0 volt signal from potentiometer R1 or a fixed 1.4 volt signal. The 1.4 volt position can be used with a pixel clock that has TTL levels. Some camera pixel clock outputs do not have TTL levels. See the Adjustments chapter for details.

| CK Position | Mark | Select                                                 |

|-------------|------|--------------------------------------------------------|

| Left        | POT  | Potentiometer for comparison of pixel clock input.     |

| Right       | 1.4  | Positive 1.4 volt for comparison of pixel clock input. |

JA1 selects pin 6 of the DB25 connector to be either an external input or an external output.

| JA1 Position | Mark | Select                    |

|--------------|------|---------------------------|

| Left         | IN   | External input selected.  |

| Right        | OUT  | External output selected. |

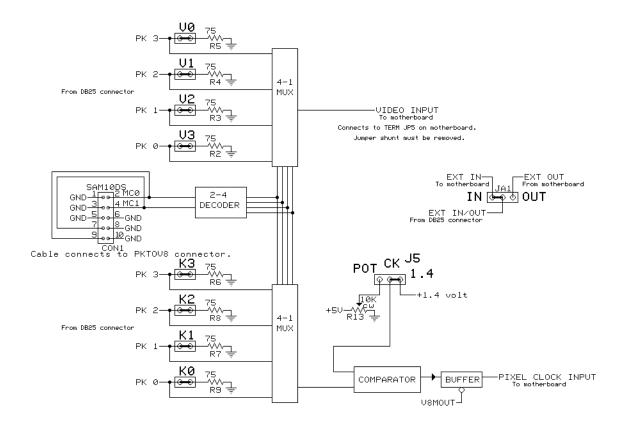

A block diagram of the Pixel Clock and Video Four Input Multiplexer is shown in Figure 3-7.

Figure 3-7. Pixel Clock and Video Four Input Multiplexer Jumpers Block Diagram

Selection of the video and pixel clock input is controlled by the T12 register bits MC1 and MC0 as shown in the table below. In 4MIP the mode control bits (MC) may be controlled by the *Camera Control Mode* in the *Video Capture & Display* menu of the *Capture* menu. On startup of 4MIP the bits are set to 0.

| MC1 | MC0 | Video Input and Pixel Clock Selected |

|-----|-----|--------------------------------------|

| 1   | 1   | VIN 3, PK 3                          |

| 1   | 0   | VIN 2, PK 2                          |

| 0   | 1   | VIN 1, PK 1                          |

| 0   | 0   | VIN 0, PK 0                          |

TABLE 3-4. Pixel Clock and Video Four Input Multiplexer Selection

To keep cross coupling of one video input to another to a minimum, it is recommended that the video inputs to the Pixel Clock and Video Four Input Multiplexer are synchronized. In other words, the video sources should have identical vertical and horizontal timing.

### 3.G Pixel Clock Generator Module

The blue, socketed module with white alphanumerics at location F7 is the pixel clock generator module (PCGM). While not a jumper, the PCGM may be user installed, similar to a jumper.

The standard Model 12 is shipped with a STTLPCGM-107 PCGM which generates a frequency of 14.318 MHz. The "S" prefix denotes that the TTL PCGM is a special frequency. The PCGM is available in standard frequencies

from 2 MHz to 10 MHz in 0.5 MHz increments, and from 10 MHz to 30 MHz in 1 MHz increments. Some of the special frequencies available are shown in Table 3-5.

Note that the PCGM is static sensitive and should be removed or installed by following static handling procedures.

A 30 MHz Model 12 can use any frequency PCGM equal to or less than 30 MHz. Similar frequency rules apply to higher frequency Model 12 boards. If square pixels are desired from a RS-170 video source, a 12 MHz PCGM is recommended.

| Clock Frequency | PCGM Part Number |

|-----------------|------------------|

| 9.204 MHz       | STTLPCGM-122     |

| 9.752 MHz       | STTLPCGM-109     |

| 11.45 MHz       | STTLPCGM-129     |

| 12.5 MHz        | STTLPCGM-117     |

| 13.3 MHz        | STTLPCGM-110     |

| 14.318 MHz      | STTLPCGM-107     |

| 21.4 MHz        | STTLPCGM-124     |

| 28.6 MHz        | STTLPCGM-250     |

| 33.33 MHz       | STTLPCGM-121     |

| 35.0 MHz        | STTLPCGM-120     |

| 40.0 MHz        | STTLPCGM-130     |

| 45.0 MHz        | STTLPCGM-131     |

| 50.0 MHz        | STTLPCGM-139     |

**TABLE 3-5.** Special PCGM Clock Frequencies and Part Numbers

| <b></b> ■ EPIX。 |  |

|-----------------|--|

|-----------------|--|

# 4. Adjustments

### 4.A Motherboard Potentiometers

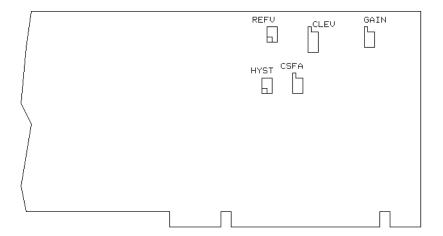

The 4MEG VIDEO Model 12 motherboard has five potentiometers. They adjust the input video gain, video clamp level, A-D reference voltage level, the sync stripper horizontal frequency detection, and when pixel clocks greater than 40 MHz are used, the hysterisis of the A-D converter.

A procedure to adjust the video gain and clamp (black) level is given in the Gain and Black Level Adjustment chapter of this manual.

Motherboard potentiometer locations are shown in Figure 4-1.

Figure 4-1. Motherboard Potentiometer Locations

The GAIN pot is used to adjust the gain of the video input amplifier. Turning the GAIN pot clockwise will increase the gain. The video input of the analog to digital converter (A-D) Analog Devices AD9048, is pin 21 with ground on pin 25. An axial capacitor marked "AGND" provides ground on both legs at location A16. For the Analog Devices AD9012 A-D, the video input is pin 5, with ground on pin 2. The input signal should be from 0 to -2V measured from the back porch of the video to maximum white level.

The CLEV (Clamp LEVel) pot is used to adjust the voltage that the video is clamped to on the video back porch. The voltage of the video back porch (between the end of horizontal drive and the beginning of active video) should be set so that the blackest portion of the video input has a 0 grey level. Turning CLEV clockwise makes the clamp voltage more positive and shifts the video input towards the zero grey level.

The REFV (REFerence Voltage) pot is used to adjust the A-D 255 grey level reference voltage. Damage to the A-D converter may take place if the reference voltage is more negative than -2.2 volts. It is normally set to -2.0 volts. Adjustment of this setting is **not recommended** and normally not required. Pin 26 of the AD9048 is the reference voltage of the A-D. The reference voltage determines the maximum white level and is the upper limit of the range of the A-D.

The CSFA (Composite Sync Frequency Adjust) pot is used to adjust the sync stripper's clamp width, vertical drive width, and field detector. When genlocking to an interlaced video format, 4MIP allows display of the decoded video

field which can be used to determine when the CSFA pot is adjusted properly. Turning the CSFA pot clockwise sets the sync stripper for lower horizontal frequency video formats.

A programmable method of decoding the horizontal and vertical timing information and clamping the video input is available in the Video Format menu of the 4MIP software for the Model 12. The menu item is called Genlock Sync and Clamp: HCM and it appears in the Custom Interface Modes menu of the Digitize Video Format menu and the Display Video Format menu of the Video Format & Resolution menu of the Setup menu of 4MIP version 2.8.

The HYST potentiometer is used to adjust the hysterisis of the AD9012 A-D converter. This pot does not normally require adjustment and only has a connection to the AD9012 which is used for pixel clock rates greater than 40 MHz.

# 4.B Analog Module Potentiometer

The Analog Module has a potentiometer to adjust the comparison voltage for the Analog Module external pixel clock input comparator. The CK jumper on the Analog Module must be in the "P" position for the potentiometer voltage to be used. Turning pot clockwise makes the comparison voltage more negative. The range of adjustment is +5 volts (CCW) to ground (CW). Adjust the potentiometer for optimum slicing of the external pixel clock input.

### 4.C Pixel Clock and Video Four Input Multiplexer Module Potentiometer

The Pixel Clock and Video Four Input Multiplexer Module has a potentiometer to adjust the comparison voltage for the module's external pixel clock input comparator. It performs the same function as does the pot on the Analog Module (above). The CK jumper (J5) on the module must be in the "POT" position for the potentiometer voltage to be used. Turning pot clockwise makes the comparison voltage more negative. The range of adjustment is +5 volts (CCW) to ground (CW). Adjust the potentiometer for optimum slicing of the external pixel clock input. Note that there is only one pot for the four pixel clock inputs which implies that the four pixel clock input voltage levels are similar.

### 5. Architecture

### 5.A Data Path

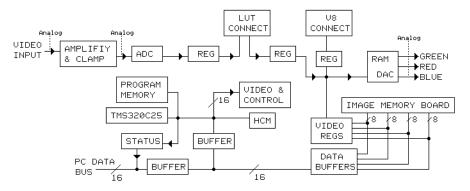

The diagram below shows the data path connections of the logic blocks of the 4MEG VIDEO Model 12. The block functions are described in the following text.

Data paths are 8 bit and bidirectional unless shown otherwise.

Figure 5-1. Data Path Block Diagram

### **5.A.1 AMPLIFY & CLAMP**

The AMPLIFY & CLAMP circuits buffer, amplify, and clamp the video input. Gain and clamp level are set with potentiometers.

### 5.A.2 ADC

The ADC (Analog to Digital Converter) converts the analog video signal to an 8 bit code on each pixel clock. The output of the ADC is connected to a register (REG) to provide additional drive capability and to allow the output to the LUT connector to be tristated.

### **5.A.3 LUT CONNECT**

To allow look up table transformations or other video rate operations, the registered ADC output connects to the LUT connector. The input from the LUT connector is registered to provide addition drive and to allow the LUT connector input to be tristated when not in digitize mode.

#### 5.A.4 V8 CONNECT

The V8 connector provides connections for 8 bit digital video input, output, and control signals.

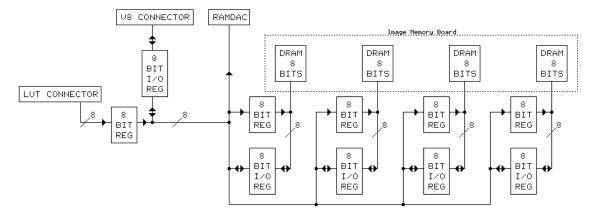

### **5.A.5 RAMDAC & CURSOR**

A set of three 256 byte look up tables (RAM) transform the 8 bit digital data into up to 2 to the 24th colors. The 24 bit output of the look up tables connect to three 8 bit digital to analog converters (DAC). Each of the DACs drive one of the GREEN, RED, or BLUE outputs of the DB25 connector. The cursor allows the video to be overlaid with a programmable size crosshair and/or a 64 by 64 one bit icon. The RAM and CURSOR are loaded by the TMS320C25.

### **5.A.6 VIDEO REGS**

The video registers allow four sequential 8 bit pixels to be loaded while the previous four pixels are written to image memory when in digitize mode. In display mode, the video registers allow four sequential 8 bit pixels to be loaded from the image memory and driven to the video bus 8 bits at a time.

### **5.A.7 IMAGE MEMORY BOARD**

The image memory is triple ported to the PC/AT bus, to the TMS320C25, and to video data (ADC input thru the LUT, RAMDAC output, and V8 connector).

#### **5.A.8 DATA BUFFERS**

The data buffers provide byte or word access to either the PC/AT bus or the TMS320C25.

### 5.A.9 TMS320C25

A 50 MHz Texas Instruments TMS320C25 digital signal processor is used to control the operation of the Model 12, to perform image processing operations, and to control the generation of the video format.

### **5.A.10 PROGRAM MEMORY**

A 32K × 16 bit static RAM program memory provides zero wait state instruction access by the TMS320C25. The PC/AT bus passes data to and from the TMS320C25 via the program memory. To allow the PC/AT bus to access image memory while the TMS320C25 executes instructions, a buffer separates the TMS320C25 and program memory from the 16 bit bus to the PC/AT buffer and to the image memory data buffers. When the PC/AT bus is accessing the TMS320C25's program memory, wait states are generated on the PC/AT bus until the TMS320C25 enters the "HOLD ACKNOWLEDGE" state.

#### **5.A.11 STATUS**

A status register is provided to allow the TMS320C25 to pass information to the PC/AT bus without disturbing the TMS320C25 data path to image memory.

#### 5.A.12 HCM

The Horizontal Control Memory (HCM) is written by the TMS320C25 with data that generates video control signals. The HCM is addressed by a counter which is incremented by the pixel clock. The registered outputs of the HCM are connected to logic devices which control data flow to and from the image memory. The HCM interfaces with the VIDEO CONTROL logic which consists of the following elements:

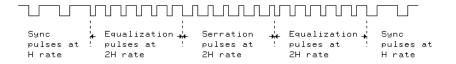

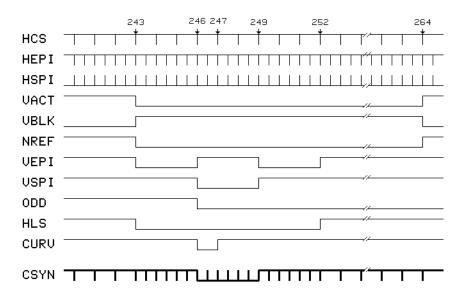

**5.A.12.a Vertical Control Register** The TMS320C25 uses the Vertical Control Register (VCR) to generate video timing signals that take place at horizontal or twice horizontal rates, such as, vertical blanking, vertical refresh, vertical sync, and the field signal. The VCR and HCM generate video sync signals.

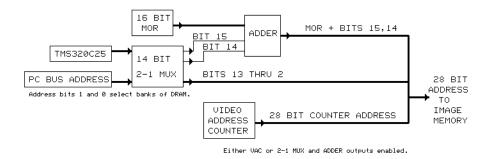

**5.A.12.b Video Address Counter** A 24 bit counter generates image memory addresses during digitize and display. The counter is loaded by the TMS320C25 usually during horizontal blanking. The counter is incremented or decremented after or prior to each image memory cycle which is a maximum of every four pixels.

**5.A.12.c Sync Logic** Composite sync may be generated by the Model 12 or may be received from a video source. The HCM and the sync logic can be used to detect vertical sync and field timing from a composite sync or composite video input.

**5.A.12.d Sync Stripper** When genlocking to composite video, composite sync, or horizontal sync, the sync stripper is used to detect video synchronization signals. It separates and regenerates horizontal, vertical, and field information from the composite input signal. It also generates a clamp signal to DC restore the video signal at the start of each line.

**5.A.12.e Pixel Clock Generator** A register and jumper select the pixel clock to be either the PC bus 14.318 MHz oscillator, an externally supplied clock, or a plug-in 2 MHz to 50 MHz pixel clock generator module.

©EPIX.

### 6. Registers and Horizontal Control Memory

Two register sets are described below. The 8 bit PC Bus I/O registers are in the PC processor I/O space. The 16 bit TMS320 I/O registers are in the TMS320 I/O space. Bits shown as "reserved" should be written with zero and masked on a read.

### 6.A PC Bus I/O Registers

The "I/O" jumper selects either 0x280 or 0x290 as the PC bus I/O base address. The PC registers below are shown with 0x280 as the base address. The I/O address decode circuit can be replaced to provide other I/O base selections.

### 0x280 (PC0) TMS320 Status Register. Read Only. Undefined at power up.

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| T3-7  | T3-6  | T3-5  | T3-4  | T3-3  | T3-2  | T3-1  | T3-0  |

Status register PC0 is written by the TMS320 as register T3. If an interrupt to the PC was enabled and waiting, a read of PC0 clears the interrupt.

### 0x281 (PC1). TMS320 Status Register. Read Only. Undefined at power up.

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| T3-7  | T3-6  | T3-5  | T3-4  | T3-3  | T3-2  | T3-1  | T3-0  |

A read of PC1 is similar to reading PC0 but does not clear a waiting interrupt. This allows the status to be read while interrupts are operational.

#### 0x281 (PC1). PC Control Register. Write Only. Cleared at power-up.

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 |

|-------|-------|-------|-------|-------|-------|--------|-------|

| PCME  | PCIM  | PC5   | PCIMA | PCENI | PCIT  | PCTRUN | PC0   |

→ PC Memory Enable → Decode PC bus memory addresses (image memory or program memory).

→ No Decode of PC bus memory addresses. 6 → PC Image Memory → Image memory selected.  $0 \rightarrow Program memory selected.$ Bit  $\rightarrow$  T0 register bit 4=1.  $\rightarrow$  T0 register bit 4=0. → PC Image Memory Access → PC Image Memory Access (when T12 bit 4 = 0).

→ TMS320 may have access. → PC ENable Interrupt

→ Enable TMS320 to PC interrupt.  $\rightarrow$  No interrupts to PC. → PC Interrupt TMS320

→ Interrupt to TMS320 on low to high transition.  $0 \rightarrow \text{No interrupt to TMS320.}$ → PC TMS320 RUN → Allow TMS320 to execute instructions.  $\rightarrow$  Reset TMS320 (low for  $\geq$ 300 ns). → PC to TMS320 T0 Register Signal (T0 bit 9) → T0 register bit 9=1  $\rightarrow$  T0 register bit 9=0.

### 0x282 (PC2). Lower Memory Offset Register (LMO). Read/Write. Undefined at power-up.

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| MO7   | MO6   | MO5   | MO4   | MO3   | MO2   | MO1   | MO0   |

#### 0x283 (PC3). Upper Memory Offset Register (UMO). Read/Write. Undefined at power-up.

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| MO15  | MO14  | MO13  | MO12  | MO11  | MO10  | MO9   | MO8   |

| MS1   | MS0   | MS1   | MS0   | MS1   | MS0   |       |       |

| 16MB  | 16MB  | 4MB   | 4MB   | 1MB   | 1MB   |       |       |

To access more than the first 64K of image memory, the PC uses a 16 bit memory offset register (MO) consisting of the UMO and LMO. The MO is shared with the TMS320. The PC can read or write the contents of the LMO or UMO register only when the PC (and not the TMS320) has access to the image memory. The contents of the MO register is added to bits 15 and 14 of the PC address to create the upper address bits to the image memory.

When the Model 12 is connected to an IMAGE MEMORY EXPANSION board, two bits of the UMO are used to select one of four groups of four memory modules on the IMAGE MEMORY EXPANSION board. A carry from the lower bits of the address does not affect the module select bits. When 16MB modules are installed, MO15 and MO14 select one of four groups of four memory modules. When 4MB modules are installed, MO13 and MO12 select one of four groups of four memory modules. When 1MB modules are installed, MO11 and MO10 select one of four groups of four memory modules.

### 6.B TMS320 I/O Registers

### 0x0 (T0) PC and Video Status Register. Read Only. Undefined at power-up.

| I | Bit 15   | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|----------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|   | Reserved |        |        |        |        |        | PCB0  | P16C  | NSVD  | SODD  | EVD   | PCB5  |       | Rese  | erved |       |

```

→ PCB0

\rightarrow PC1 register bit 0 (PCB0) = 1.

\rightarrow PC1 register bit PCB0 = 0.

\rightarrow P16C

Bit

→ PC bus 16 bit bus memory cycles available.

→ PC bus 8 bit bus cycles.

\rightarrow NSVD

Bit

→ Not vertical drive from sync stripper or sync detect (selected by SYCL, T13).

→ Vertical drive from sync stripper or sync detect.

\rightarrow SODD

Bit

→ Odd field from sync stripper or sync detect (selected by SYCL, T13).

→ Even field from sync stripper or sync detect.

\rightarrow External vertical drive from V8 or DB25 connector = 1.

\rightarrow Vertical drive from V8 or DB25 connector = 0.

\rightarrow PCB5

\rightarrow PC1 register bit 5 (PCB5) = 1.

\rightarrow PC1 register bit PCB5 = 0.

```

Register T0 can be used by TMS320 software to determine the state of vertical sync, video field, and the state of bits 5 and 0 of register PC1. The sync stripper vertical sync may be selected to be from either the sync stripper or an on-board programmable vertical sync and field detector. The programmable vertical sync and field detector is selected with bit 3 of register T13 (SYCL). The field signal is selected from either the sync stripper or the on-board programmable vertical sync and field detector. Bits PCB5 and PCB0 from register PC1 provide communication between the PC and the TMS320.

#### 0x0 (T0) Interrupt PC. Write Only.

| Bit 15 | Bit 14      | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|-------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|        | Don't care. |        |        |        |        |       |       |       |       |       |       |       |       |       |       |

Writing to T0 when PC interrupts are enabled generates an interrupt to the PC.

## 0x1 (T1) Control Register 1. Write Only. Cleared at power-up.

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| MEMS   | HLLE   | HS1K   | НСМЕ   | HCMG   | PHS0   | ADS1  | ADS0  | HS16K | HS4K  | PHS1  | UNBK  | Rsvd  | Rsvd  | Rsvd  | DEC   |

| Bit |        |               | 15            | $\rightarrow$                             | MEMory Select                                                             |

|-----|--------|---------------|---------------|-------------------------------------------|---------------------------------------------------------------------------|

|     |        |               | 1             | $\rightarrow$                             | Select image memory.                                                      |

|     |        |               | Ō             | $\rightarrow$                             | Select horizontal control memory.                                         |

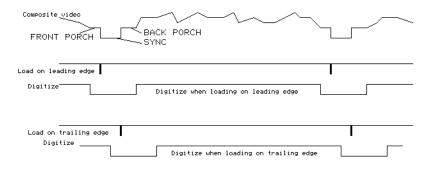

| Bit |        |               | 14            | $\rightarrow$                             | HCM starting address Load on Leading Edge                                 |

|     |        |               | 1             | $\rightarrow$                             | Load HCM start addr. on leading edge of input sync when in genlock mode.  |

|     |        |               | ō             | $\rightarrow$                             | Load HCM start addr. on trailing edge of input sync when in genlock mode. |

| Bit |        |               | 13            | $\rightarrow$                             | Horizontal Starting address 1K                                            |

|     |        |               |               |                                           | -see bits 7 and 6 below                                                   |

| Bit |        |               | 12            | $\rightarrow$                             | HCM Enable                                                                |

|     |        |               | 1             | $\rightarrow$                             | Enable HCM counters.                                                      |

|     |        |               | ō             | $\rightarrow$                             | Disable HCM counters, and load HCM counters with starting address.        |

| Bit |        |               | 11            | $\rightarrow$                             | Horizontal Control Memory Gate                                            |

|     |        |               | 1             | <b>→</b>                                  | HCM SMC to image memory allowed.                                          |

|     |        |               | Õ             | $\rightarrow$                             | HCM SMC to image memory not allowed.                                      |

| Bit |        |               | 10            | $\rightarrow$                             | Pixel clock and Horizontal load Select 0                                  |

| Dit |        |               | 10            |                                           | -see bit 5 below                                                          |

| Bit |        | 9             | 8             | $\rightarrow$                             | Address Select 1, 0                                                       |

| ш   |        | Ó             | 0             | $\rightarrow$                             | RAMDAC Addr Register and Cursor Addr Register 0.                          |

|     |        | 0             | 1             | $\rightarrow$                             | RAMDAC Color Palette RAM and Cursor Addr Register 1.                      |

|     |        | 1             | 0             | $\rightarrow$                             | RAMDAC Addr Register and Cursor RAM.                                      |

|     |        | 1             | 1             | $\rightarrow$                             | RAMDAC Overlay Register and Cursor Control Register.                      |

| Bit | 13     | 7             | 6             | $\rightarrow$                             | Horizontal control memory Starting Address                                |

|     | 0      | 0             | 0             | $\rightarrow$                             | $0 \qquad (0x0000)$                                                       |

|     | 0      | 0             | 1             | $\rightarrow$                             | 1024 (0x0400)                                                             |

|     | 0      | 1             | 0             | $\rightarrow$                             | 4096 (0x1000)<br>5120 (0x1400)                                            |

|     | 0<br>1 | $\frac{1}{0}$ | $\frac{1}{0}$ | $\rightarrow$                             | 5120 (0x1400)<br>16384 (0x4000)                                           |

|     | 1      | 0             | 1             | $\stackrel{\longrightarrow}{\rightarrow}$ | 17408 (0x4400)                                                            |

|     | 1      | 1             | 0             | $\stackrel{ ightarrow}{ ightarrow}$       | 20480 (0x5000)                                                            |

|     | 1      | 1             | 1             | $\stackrel{\frown}{\rightarrow}$          | 21504 (0x5400)                                                            |

|     |        | PHS1          | PHS0          |                                           |                                                                           |

| Bit |        | 5             | 10            | $\rightarrow$                             | Pixel clock and Horizontal load Select 1 and 0                            |

|     |        | 0             | 0             | $\rightarrow$                             | PC bus 14.318 MHz clock and HCM load (master).                            |

|     |        | 0             | 1             | $\rightarrow$                             | Pixel Clock Gen. Module (PCGM) clock and PCGM load (genlock).             |

|     |        | 1             | 0             | $\rightarrow$                             | Pin 1 of DIC clock and HCM load (external 0).                             |

|     |        | 1             | 1             | $\rightarrow$                             | Pin 1 of DIC clock and pin 9 of DIC load (external 1).                    |

| Bit |        |               | 4             | $\rightarrow$                             | UNBLANK                                                                   |

|     |        |               | 1             | $\rightarrow$                             | Unblank RAMDAC Video Output                                               |

|     |        |               | 0             | $\rightarrow$                             | Blank RAMDAC Video Output                                                 |

| Bit |        | 3             | 2             | $\rightarrow$                             | Reserved (previously HAR clock select).                                   |

| Bit |        |               | 1             | $\rightarrow$                             | Reserved (previously the Fast TMS access bit).                            |

| Bit |        |               | 0             |                                           | DECrement image memory address                                            |

|     |        |               | 1             | $\rightarrow$                             | DECrement image memory address Decrement image memory address after SMC.  |

|     |        |               | 0             | $\rightarrow$                             | Increment image memory address after SMC.                                 |

#### 0x2 (T2) Bit Plane Write Register. Write Only. Undefined at power-up.

| Bit | 15       | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|----------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|     | Reserved |        |        |        |        |        |       |       | BPW7  | BPW6  | BPW5  | BPW4  | BPW3  | BPW2  | BPW1  | BPW0  |

The Bit Plane Write register enables image memory bit planes for processor or HCM digitize writes to the image memory. When BPW7=1, bit 7 of the image memory is write enabled. When BPW7=0, bit 7 of the image memory is write disabled. When BPW6=1, bit 6 of the image memory is write enabled, etc. Bit Plane Write does not work with image memory boards with fewer than 32 DRAMs (such as the 4MB image memory board) and must have 0xFF loaded to operate properly.

### 0x3 (T3) TMS320 Status Register. Write Only. Undefined at power-up.

| Bit 15 | Bit 14   | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|----------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|        | Reserved |        |        |        |        |       |       |       | T3-6  | T3-5  | T3-4  | T3-3  | T3-2  | T3-1  | T3-0  |

The PC reads this register as PC0. It provides TMS320 to PC communication.

#### 0x4 (T4) Video Address Counter Low. Write Only. Undefined at power-up.

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| VA15   | VA14   | VA13   | VA12   | VA11   | VA10   | VA9   | VA8   | VA7   | VA6   | VA5   | VA4   | VA3   | VA2   | VA1   | VA0   |

#### 0x5 (T5) Video Address Counter High. Write Only. Undefined at power-up.

| Bit 15 | Bit 14   | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|----------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|        | Reserved |        |        |        | VA26   | VA25  | VA24  | VA23  | VA22  | VA21  | VA20  | VA19  | VA18  | VA17  | VA16  |

The 28 bit video address counter provides the image memory address for video digitize or display. Writes to the counters must take place when the SMC bit of the HCM is not generating image memory cycles (when HCBL=0, VBL=0, or when the HCM is disabled). Usually, the TMS320 writes the counters once per line or once per field. The T4 counter contains the low 16 bits of the image memory address. The T5 counter contains the upper 8 bits of the image memory address. The counters address the image memory as four pixels (32 bits). HCM bits Bf1 and Bf0 provide one of four pixel selection. See the Architecture chapter for details.

### 0x6 (T6) Memory Offset Register. Write/Read. Undefined at power-up.

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| MO15   | MO14   | MO13   | MO12   | MO11   | MO10   | MO9   | MO8   | MO7   | MO6   | MO5   | MO4   | MO3   | MO2   | MO1   | MO0   |

The MO register is used by the TMS320 and the PC to access more than the first 64KB of the image memory address space. The MO register can be written and read by both the PC and the TMS320. The processor with access to the image memory also has access to the MO register. The contents of the MO register is added to bits 15 and 14 of the processor address to form the image memory address.

When the Model 12 is connected to an IMAGE MEMORY EXPANSION board, two bits of the MO are used to select one of four groups of four memory modules on the IMAGE MEMORY EXPANSION board. A carry from the lower bits of the address does not affect the module select bits. When 16MB modules are installed, MO15 and MO14 select one of four groups of four memory modules. When 4MB modules are installed, MO13 and MO12 select one of four groups of four memory modules. When 1MB modules are installed, MO11 and MO10 select one of four groups of four memory modules.

#### 0x7 (T7) Clock Vertical Control Output Register. Read.

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|        |        |        |        |        |        |       | Not ' | Valid |       |       |       |       |       |       |       |

A read of T7 causes the contents of the Vertical Control Input Register (see below) to be loaded into the Vertical Control Output Register. See the section on the VCR for details. Data read by the TMS320 is invalid.

#### 0x7 (T7) Vertical Control Input Register. Write. Undefined at power-up.

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|        |        |        | R      | es     |        |       |       | HLS   | ODD   | Res   | VEPI  | VSPI  | VACT  | CURV  | NREF  |

|        |        |        | R      | es     |        |       |       | (HLS) | (ODD) |       | (EPI) | (SPI) | (FLW) | (CUR) | (REF) |

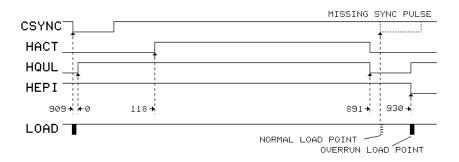

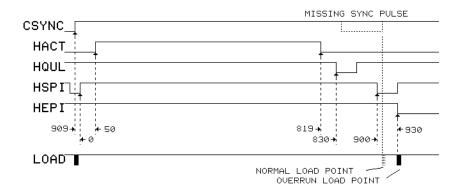

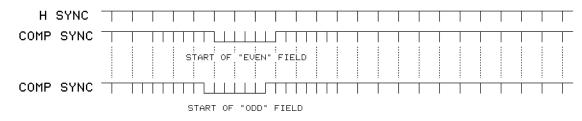

| Bit        |                       | 7<br>1<br>0           | → Half Line Select  → Select HCM bit 7 (HCS) as TMS320 level 0 interrupt.  → Select HCM bit 1 (HCSEPI) as TMS320 level 0 interrupt.                                                                                                                                        |